What is the story about?

QpiAI, an Indian company developing AI and quantum computing solutions, on Wednesday, March 25, unveiled a high-speed decoder hardware platform for real-time quantum error correction on superconducting processors.

This major advancement in quantum error correction (QEC) significantly reduces error detection and correction times, a significant step toward the development of scalable, practical quantum computers.

The breakthrough was demonstrated on QpiAI’s 64-qubit Kaveri superconducting quantum processor. According to the company, the newly developed decoder reduces the time required for error correction from tens of microseconds using conventional software approaches to approximately 1.5 microseconds per cycle.

This improvement addresses one of the key challenges in

quantum computing,

where errors must be corrected quickly within the short coherence time of qubits. This platform implements a distance-5 rotated surface code using 49 physical qubits.

Each decoder operates on a single Kaveri quantum processing unit (QPU), allowing efficient decoding and integration with existing quantum hardware and enabling real-time performance.

QpiAI founder and CEO Nagendra Nagaraja said the platform demonstrates a practical path toward hardware-accelerated quantum error correction, reducing reliance on traditional computing systems such as CPUs and GPUs.

“The performance of our new decoder platform demonstrates a practical pathway toward scalable, hardware-accelerated quantum error correction. Compatible with widely used superconducting transmon qubits, the platform limits the need for additional classical support from CPUs and GPUs,” he said.

The company is also working on next-generation error correction techniques “tailored to our own fluxonium-based qubits as well as architectures designed to operate across distributed systems,” Nagaraja added.

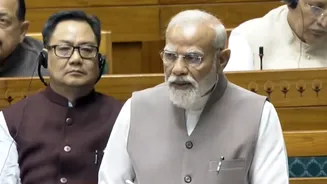

The project has received partial support from India’s National Quantum Mission. QpiAI has achieved a significant milestone in developing quantum technologies, according to Dr Abhay Karandikar, Secretary of the Department of Science and Technology (DST). This advancement supports the government’s national initiative to deploy quantum technologies.

Why it's important

He noted that hardware-based error correction is crucial for advancing large-scale quantum computing capabilities in the country.

“By implementing distance-5 surface code QEC in custom hardware rather than traditional CPUs, QpiAI is accelerating the deployment of its 64-qubit Kaveri QPU in India, marking a major step toward practical, large-scale quantum utility,” Karandikar added.

Beyond its high-speed decoder, QpiAI's quantum processors incorporate error-correction architecture and optimised superconducting quantum processor layout and fabrication. The decoder platform also makes use of QpiAISense quantum control electronics, allowing for the scalable creation of quantum processors that lead to fault-tolerant quantum computing.

The decoder platform enables multiple rounds of stabiliser measurements in each cycle, allowing detection of both qubit and measurement errors. With coherence times reaching 100 microseconds (T1) and 95 microseconds (T2), the platform allows for multiple error correction cycles before errors accumulate, enhancing overall computational reliability.

The company plans to showcase demonstrations of the technology in the coming months, including at its facilities in the United States.

This major advancement in quantum error correction (QEC) significantly reduces error detection and correction times, a significant step toward the development of scalable, practical quantum computers.

The breakthrough was demonstrated on QpiAI’s 64-qubit Kaveri superconducting quantum processor. According to the company, the newly developed decoder reduces the time required for error correction from tens of microseconds using conventional software approaches to approximately 1.5 microseconds per cycle.

This improvement addresses one of the key challenges in

Each decoder operates on a single Kaveri quantum processing unit (QPU), allowing efficient decoding and integration with existing quantum hardware and enabling real-time performance.

QpiAI founder and CEO Nagendra Nagaraja said the platform demonstrates a practical path toward hardware-accelerated quantum error correction, reducing reliance on traditional computing systems such as CPUs and GPUs.

“The performance of our new decoder platform demonstrates a practical pathway toward scalable, hardware-accelerated quantum error correction. Compatible with widely used superconducting transmon qubits, the platform limits the need for additional classical support from CPUs and GPUs,” he said.

The company is also working on next-generation error correction techniques “tailored to our own fluxonium-based qubits as well as architectures designed to operate across distributed systems,” Nagaraja added.

The project has received partial support from India’s National Quantum Mission. QpiAI has achieved a significant milestone in developing quantum technologies, according to Dr Abhay Karandikar, Secretary of the Department of Science and Technology (DST). This advancement supports the government’s national initiative to deploy quantum technologies.

Why it's important

He noted that hardware-based error correction is crucial for advancing large-scale quantum computing capabilities in the country.

“By implementing distance-5 surface code QEC in custom hardware rather than traditional CPUs, QpiAI is accelerating the deployment of its 64-qubit Kaveri QPU in India, marking a major step toward practical, large-scale quantum utility,” Karandikar added.

Beyond its high-speed decoder, QpiAI's quantum processors incorporate error-correction architecture and optimised superconducting quantum processor layout and fabrication. The decoder platform also makes use of QpiAISense quantum control electronics, allowing for the scalable creation of quantum processors that lead to fault-tolerant quantum computing.

The decoder platform enables multiple rounds of stabiliser measurements in each cycle, allowing detection of both qubit and measurement errors. With coherence times reaching 100 microseconds (T1) and 95 microseconds (T2), the platform allows for multiple error correction cycles before errors accumulate, enhancing overall computational reliability.

The company plans to showcase demonstrations of the technology in the coming months, including at its facilities in the United States.